## Description

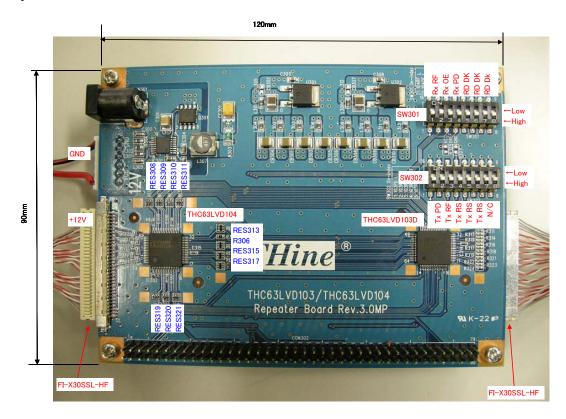

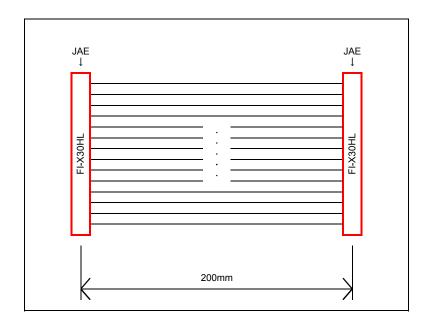

## LVDS-Cable Type.

**SW301 Setting**

\* Def. : Default Setting

| SW   | *     |          | THC63LVD104S |                                                                                 |                                                                          |         |         |                      |  |  |  |  |

|------|-------|----------|--------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------|---------|----------------------|--|--|--|--|

| Pin# | Def.  | NodeName | IC<br>Pin#   | PinName                                                                         | Description                                                              |         |         |                      |  |  |  |  |

| 1    | Н     | Rx RF    | 5            | R/F                                                                             | Output Clock Tri<br>H : Rising Edge<br>L : Falling Edge                  |         |         |                      |  |  |  |  |

| 2    | Н     | Rx OE    | 4            | OE                                                                              | Output Enable.<br>H : Output enable.<br>L : Output disable.              |         |         |                      |  |  |  |  |

| 3    | Н     | Rx PD    | 3            | PD                                                                              | Power down and Output Control.<br>H : Normal operation<br>L : Power down |         |         |                      |  |  |  |  |

| 4    | Н     |          |              | Output Clock Delay Timing Select. tRCP=Output Clock Cvcle  SW-Pin# Offset[sees] |                                                                          |         |         |                      |  |  |  |  |

|      |       |          |              |                                                                                 | 4                                                                        | 5       | 6       | Offset[nsec]         |  |  |  |  |

| 5    | Н     | Rx DK    | 2            | DK                                                                              | L                                                                        | H(open) | H(open) | 3 <u>tRCP</u><br>14  |  |  |  |  |

|      |       |          |              |                                                                                 | H(open)                                                                  | L       | H(open) | -3 <u>tRCP</u><br>14 |  |  |  |  |

| 6    | L     |          |              |                                                                                 | H(open)                                                                  | H(open) | L       | 0                    |  |  |  |  |

|      |       |          |              |                                                                                 |                                                                          |         |         |                      |  |  |  |  |

| 7    | Н     |          | N/O          |                                                                                 | Non Connected                                                            |         |         |                      |  |  |  |  |

| 8    | H N/C | N/C      | _            | _                                                                               |                                                                          |         |         |                      |  |  |  |  |

### **SW302 Setting**

\* Def. : Default Setting

| 311  | JUZ  | Setting | )          |         |               |                                                                            |              |            |                         | 201.                 | Delault oetting |  |

|------|------|---------|------------|---------|---------------|----------------------------------------------------------------------------|--------------|------------|-------------------------|----------------------|-----------------|--|

| SW   | *    | Node    |            |         |               | THC63LVD                                                                   | THC63LVD103D |            |                         |                      |                 |  |

| Pin# | Def. | Name    | IC<br>Pin# | PinName | Description   |                                                                            |              |            |                         |                      |                 |  |

| 1    | Н    | Tx PD   | 13         | /PDWN   |               | H : Normal operation,<br>.: Power down (all outputs are Hi-Z)              |              |            |                         |                      |                 |  |

| 2    | Н    | Tx RF   | 60         | R/F     | H : Rising    | nput Clock Triggering Edge Select.<br>H : Rising edge,<br>L : Falling edge |              |            |                         |                      |                 |  |

| 3    | Н    |         | 43         | RS      | LVDS swi      | SW-Pina<br>4                                                               |              | ct.<br>RS  | RS LVDS Swing Small Swi |                      |                 |  |

| 4    | Н    | Tx RS   |            |         | L             | H(open                                                                     | H(open)      | VCC        | 350mV                   | N/A                  |                 |  |

|      |      |         |            |         | Н(оре         | n) L                                                                       | H(open)      | 0.6 ~ 1.4V | 350mV                   | RS=VREF <sup>a</sup> |                 |  |

| 5    | i    |         |            |         | Н(оре         | n) H(open                                                                  | L            | GND        | 200mV                   | N/A                  |                 |  |

| 5    | L    |         |            |         | a.) VF        | a.) VREF is Input Reference Voltage.                                       |              |            |                         |                      |                 |  |

| 6    | Н    |         |            |         |               |                                                                            |              |            |                         |                      |                 |  |

| 7    | Н    | N/C     | _          | _       | Non Connected |                                                                            |              |            |                         |                      |                 |  |

| 8    | Н    |         |            |         |               |                                                                            |              |            |                         |                      |                 |  |

# **Measures Type**

| # | Туре                                                  | Un-Mount                                                                                                           | 0Ω-Mount                                                                                                 | 33Ω-Mount                                                                                                            |

|---|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1 | TTL-I/O THC63LVD104 S THC63LVD103 D LVDS-output       | RES301<br>RES302<br>RES303<br>RES304<br>RES305<br>RES306<br>RES307<br>RES312<br>RES314<br>RES316<br>R308           |                                                                                                          | RES308<br>RES309<br>RES310<br>RES311<br>RES313<br>RES315<br>RES317<br>RES318<br>RES319<br>RES320<br>RES320<br>RES321 |

| 2 | THC63LVD104 S  THC63LVD103 LVDS-output D  TTL-moniter |                                                                                                                    | RES301<br>RES302<br>RES303<br>RES304<br>RES305<br>RES306<br>RES307<br>RES312<br>RES314<br>RES316<br>R308 | RES308<br>RES309<br>RES310<br>RES311<br>RES313<br>RES315<br>RES317<br>RES318<br>RES319<br>RES320<br>RES321<br>R306   |

| 3 | TTL-I/O THC63LVD104 S TTL-output                      | THC63LVD103D                                                                                                       | RES301<br>RES302<br>RES303<br>RES304<br>RES305<br>RES306<br>RES307<br>RES312<br>RES314<br>RES316<br>R308 | RES308<br>RES309<br>RES310<br>RES311<br>RES313<br>RES315<br>RES317<br>RES318<br>RES319<br>RES320<br>RES321<br>R306   |

| 4 | THC63LVD104 S THC63LVD103 LVDS-output D TTL-input     | RES308<br>RES309<br>RES310<br>RES311<br>RES313<br>RES315<br>RES317<br>RES318<br>RES319<br>RES320<br>RES321<br>R306 | RES301<br>RES302<br>RES303<br>RES304<br>RES305<br>RES306<br>RES307<br>RES312<br>RES314<br>RES316<br>R308 |                                                                                                                      |

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. We are not responsible for possible errors and omissions in this material. Please note if errors or omissions should be found in this material, we may not be able to correct them

- 3. This material contains our copy right, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without our prior permission is prohibited.

- 4. Note that if infringement of any third party's industrial ownership should occur by using this product, we will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. This product is presumed to be used for general electric equipment, not for the applications which require very hi reliability (including medical equipment directly concerning people's life, aerospace equipment, or nuclear contro equipment). Also, when using this product for the equipment concerned with the control and safety of the transportation means, the traffic signal equipment, or various Types of safety equipment, please do it after applying appropriate measures to the product.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have suffici redundant or error preventive design applied to the use of the product so as not to have our product cause any sox or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic good under the Foreign Exchange and Foreign Trade Control Law.

THine Electronics, Inc.

sales@thine.co.jp